Imagination opens up its MIPS architecture to universities

Imagination Technologies, which has two design centres in the SouthWest region, is opening up its MIPS architecture to universities with the RTL implementation of a simplified microAptiv design.

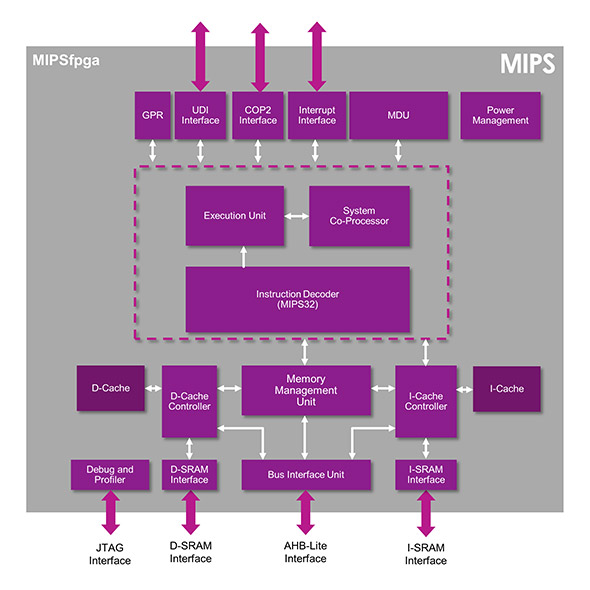

MIPSfpga gives universities around the globe free and open access to a fully-validated, current generation MIPS CPU in a complete teaching package that can be run in a low cost FPGA. The core is already popular in the PIC32MZ microcontroller from Microchip Technology but access to the detailed RTL – the code that implements the core – can be tremendously helpful for teaching.

CPU architecture is generally taught as part of electronic engineering, computer science and computer engineering courses. Until now, what’s been missing from all of these courses is access to real, un-obfuscated RTL code that will enable professors and students to study and explore a real CPU. RTL code is often hidden, or obfuscated, to prevent it being copied and used in other designs without paying royalties or license fees to the original developer.

The MIPS architecture was originally developed at Stanford University in the early 1980s. It has been the teaching architecture of choice for decades because of its elegant true RISC design, epitomized by Dr. David A. Patterson and Dr. John L. Hennessy in their book, ‘Computer Organization and Design’, now in its fifth edition.

The MIPS CPU is being offered as part of a complete free-to-download package for universities, together with a Getting Started Guide, teaching guide for professors, and examples designed to enable students to see how the CPU works and explore its capabilities. With the materials, students can develop a CPU and take it through debug, running on an FPGA platform.

This MIPS CPU configuration is designed to run on a low-cost FPGA platform, with guides available for the Digilent Nexys4 platform with a Xilinx Artix-7 FPGA, and the Terasic DE2 platform with an Altera Cyclone FPGA.

MIPSfpga is already running in several academic institutions including Harvey Mudd College, Imperial College London, University College London (UCL), and the University of Nevada, Las Vegas (UNLV).

The MIPSfpga CPU and related materials are available for download from the Imagination University Programme website now for first phase users via an application process. Academics can register at http://community.imgtec.com/university.

Phase two, starting in June, will require only a simple click-through agreement. Additional teaching materials are being developed and will be made available later this year.

However, the programme is not entirely open source. For academic users the license is simple: you can use it as you wish, but you cannot put it into silicon. If you modify it, you must talk to Imagination first if you wish to patent the changes. In summary, universities can go as deep as they like under the hood to explore how today’s complex CPUs are built.