Pulsic shows first complete automated layout tool for transistor-level analogue and custom digital designs

Bristol-based design tool developer Pulsic has launched a patent-pending technology that for the first time creates multiple electrically-correct layouts directly from schematics, allowing designers to quickly explore multiple results concurrently.

The company is demonstrating the Animate tool for the first time at the Design Automation Conference in San Francisco this week.

Existing approaches to automating analogue and custom digital integrated circuit (IC) designs have attempted to improve on portions of the design flow, but have not managed to generate “manual-quality” layout without significant user intervention. Pulsic has drawn on over a decade of experience helping leading-edge customers such as memory chip designers with physical design challenges to deliver a completely automated solution that overcomes the problem for analogue and custom-design layout.

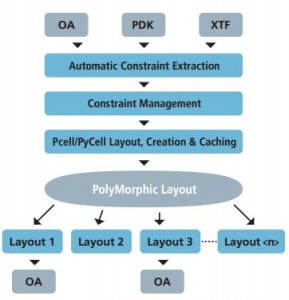

Animate is the first complete automated layout system built from the ground up for transistor-level analogue and custom-digital design. It offers designers a simple, easy-to-use layout solution that delivers multiple layouts from a schematic using automatic constraint extraction and considers place and route concurrently, producing optimal-quality results. Animate automatically generates constraints based on netlist topology analysis, eliminating the need for time-consuming manual constraint entry and management.

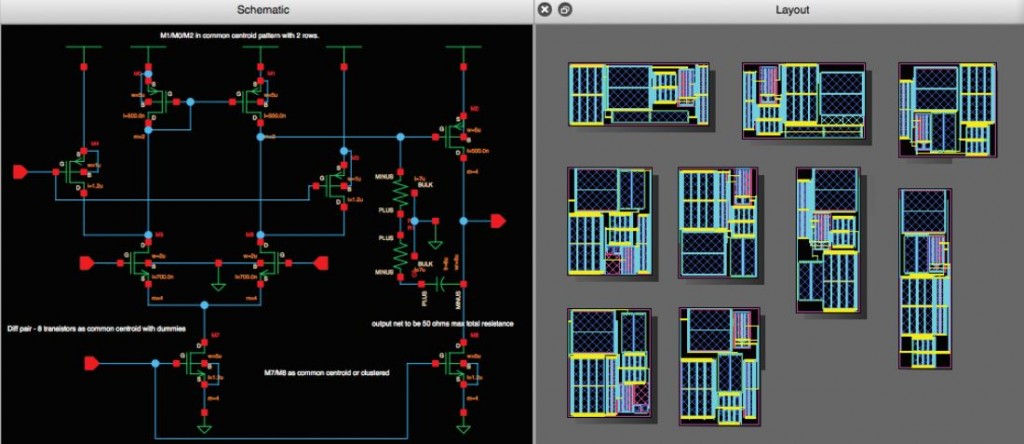

Unlike any other analogue layout system, Animate uses a novel patent-pending technology it calls PolyMorphic Layout with a database and algorithmic architecture that derives many potential layout variations for a design. These variations crystallize into multiple, complete, DRC/LVS-correct layouts in minutes. Designers can explore these complete layout options in a fraction of the time needed to produce just a single layout option by hand. As Animate produces layout results quickly, parasitics are available for simulation early in the design process, further speeding the entire design cycle. Animate places and routes simultaneously, ensuring that each process is informed by the other and that “manual-quality” results are achieved.

“As geometries shrink, and as leading-edge processes such as FinFETS reach the market, manual analogue design is no longer sufficient,” said Mark Williams, co-founder and CEO of Pulsic. “To get routable placement, you need to know what the routing will look like, but if you place and then route, you can’t know this. As DRC rules increase, iterations between layout and design are becoming onerous, but with Animate, you can generate multiple layouts, extract them all, and then choose the optimal one for the desired performance criteria. A much bigger problem space can be explored, with better results”

Designers can use Animate at an early design stage, with minimal constraints, to explore possible layout architectures and extract early parasitics for simulation of layout-dependent effects (LDE). This approach can also provide far more accurate analogue block/design size estimation during floorplanning than has ever previously been possible.

With Animate, transistor-level designers gain not only the productivity of automation, but also the ability to explore many more design options, faster than ever before. The final result is comparable to that of an expert manual layout, but is produced in a fraction of the time.

More details are on the datasheet (registration required)