Pulsic shows first complete automated layout tool for transistor-level analogue and custom digital designs

Bristol-based design tool developer Pulsic has launched a patent-pending technology that for the first time creates multiple electrically-correct layouts directly from schematics, allowing designers to quickly explore multiple results concurrently.

The company is demonstrating the Animate tool for the first time at the Design Automation Conference in San Francisco this week.

Existing approaches to automating analogue and custom digital integrated circuit (IC) designs have attempted to improve on portions of the design flow, but have not managed to generate “manual-quality” layout without significant user intervention. Pulsic has drawn on over a decade of experience helping leading-edge customers such as memory chip designers with physical design challenges to deliver a completely automated solution that overcomes the problem for analogue and custom-design layout.

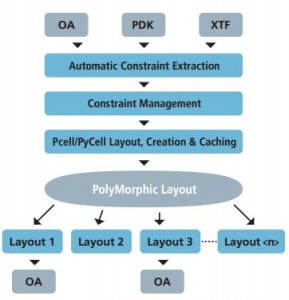

Animate is the first complete automated layout system built from the ground up for transistor-level analogue and custom-digital design. It offers designers a simple, easy-to-use layout solution that delivers multiple layouts from a schematic using automatic constraint extraction and considers place and route concurrently, producing optimal-quality results. Animate automatically generates constraints based on netlist topology analysis, eliminating the need for time-consuming manual constraint entry and management.

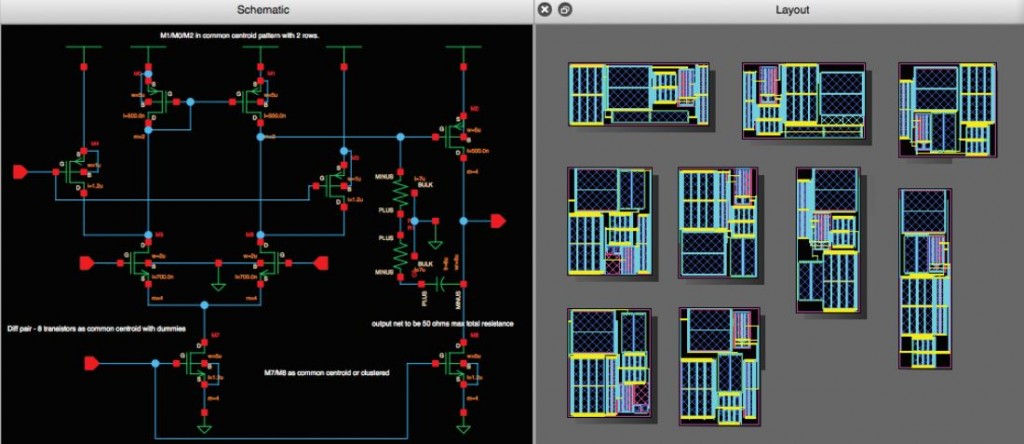

Unlike any other analogue layout system, Animate uses a novel patent-pending technology it calls PolyMorphic Layout with a database and algorithmic architecture that derives many potential layout variations for a design. These variations crystallize into multiple, complete, DRC/LVS-correct layouts in minutes. Designers can explore these complete layout options in a fraction of the time needed to produce just a single layout option by hand. As Animate produces layout results quickly, parasitics are available for simulation early in the design process, further speeding the entire design cycle. Animate places and routes simultaneously, ensuring that each process is informed by the other and that “manual-quality” results are achieved.

“As geometries shrink, and as leading-edge processes such as FinFETS reach the market, manual analogue design is no longer sufficient,” said Mark Williams, co-founder and CEO of Pulsic. “To get routable placement, you need to know what the routing will look like, but if you place and then route, you can’t know this. As DRC rules increase, iterations between layout and design are becoming onerous, but with Animate, you can generate multiple layouts, extract them all, and then choose the optimal one for the desired performance criteria. A much bigger problem space can be explored, with better results”

Designers can use Animate at an early design stage, with minimal constraints, to explore possible layout architectures and extract early parasitics for simulation of layout-dependent effects (LDE). This approach can also provide far more accurate analogue block/design size estimation during floorplanning than has ever previously been possible.

With Animate, transistor-level designers gain not only the productivity of automation, but also the ability to explore many more design options, faster than ever before. The final result is comparable to that of an expert manual layout, but is produced in a fraction of the time.

More details are on the datasheet (registration required)

Related articles

Swindon Silicon Systems celebrates 35 years of technology

ASIC designer SWINDON Silicon Systems is celebrating thirty five years of trading. From small beginnings in 1978 in Swindon, the company has grown to become the UK’s largest fabless supplier of high performance mixed signal Application Specific Integrated Circuits (ASICs) with a turnover of £21m and delivering 50 million ASICs annually. ASICs allow almost any analogue or digital circuit to be implemented on a single chip, replacing traditional discrete components. Only a few years ago a bespoke integrated circuit was no more than a dream for most industrial designers, but SWINDON has put them within the reach of any technology sector.

By 1987 SWINDON had set up a test department and moved to its current premises with a separate production facility added in 1999. The company’s success in the automotive market led to it becoming part of Tomkins Plc in 2007, assisting it’s sister company, Schrader Electronics, to become the global leader in tyre pressure monitoring systems. Schrader International was acquired by Madison Dearborn Partners in 2012, bringing SWINDON the benefits of being part of a large multinational whilst maintaining its autonomy to pursue other markets. SWINDON is expecting its growth to continue, and a move to a new custom built facility is planned to accommodate this growth.

Bristol information day on ENIAC innovation programme

The European ENIAC Programme launched its 4th call for proposals (ENIAC Call – 2011) on On February 23rd, and the Technology Strategy Board are investing over £1m into this year’s call. The programme is aimed at companies engaged in research or design for microelectronics, nanoelectronics, micromachined systems (MEMS), System in Package (SiP), and System on Chip (SoC) design.

To help South West companies prepare of their proposals, the Electronics Knowledge Centre, in partnership with the NMI and the Microelectronics iNet, is holding an information day in Bristol on March 17th at the University of the West of England (UWE). This event will provide companies an opportunity to learn about the ENIAC programme, how to apply, and how to find the right collaborative partners.

The event will also include the opportunity for companies to “pitch” their capability, particulary if they are looking to participate in the programme. This will be followed by a brokerage session, giving companies the opportunity to discuss project ideas during private “one to one” meetings.

March 17th

University of the West of England, Bristol

Speakers from: ENIAC JU, Technology Strategy Board, University of Sheffied, Philips BV

in association with NMI and the South West Microelectronics iNET

Registration fee: £15 + VAT (Members)

£30 + VAT (Non Members)